Applied Materials introduceerde gisteren nieuwe technologieën en mogelijkheden om klanten te helpen hun technologische roadmaps voor heterogene chipontwerpen en -integratie te versnellen. Daartoe verbetert Applied zijn technologieën op het gebied van geavanceerde packaging en substraten door samen te werken met de industriepartners BE Semiconductor Industries N.V. (Besi) en EVG. Zo komt het Amerikaanse bedrijf sneller tot oplossingen die verbeteringen opleveren op het gebied van vermogen, prestaties, oppervlakte, kosten en time-to-market (PPACt). Aldus berichtgeving van Semiconductor Digest.

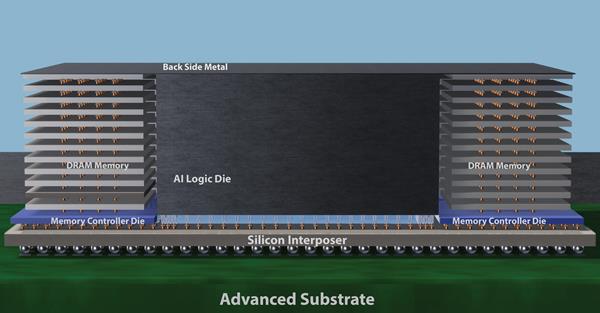

Integratie van technologieën biedt halfgeleider- en systeembedrijven nieuwe ontwerp- en productieflexibiliteit doordat chips met verschillende technologieën, functies en afmetingen in één pakket kunnen worden geïntegreerd. Applied is reeds de grootste leverancier van geavanceerde packagingtechnologieën met geoptimaliseerde producten die etsen, fysische dampdepositie (PVD), chemische dampdepositie (CVD), galvaniseren, oppervlaktebehandelingen en gloeien omvatten. Het Advanced Packaging Development Center van Applied in Singapore huisvest het breedste portfolio van producten die de fundamentele bouwstenen van heterogeneous integration mogelijk maken, waaronder geavanceerde bump en micro-bump, fine-line redistribution layer (RDL), TSV en hybrid bonding.

“Applied’s toonaangevende portfolio van geavanceerde packaging-oplossingen biedt klanten de breedste selectie van technologieën voor heterogene integratie”, zegt Nirmalya Maity, Corporate Vice President Advanced Packaging bij Applied Materials. “Door technologische co-optimalisatie en samenwerking met anderen in de industrie, bouwen we aan een ecosysteem dat de roadmaps van onze klanten kan versnellen en opwindende nieuwe groeimogelijkheden voor Applied kan creëren.”

Gisteren onthulde Applied innovaties op drie gebieden die cruciaal zijn voor geavanceerde verpakkingen voor heterogeneous integration: die-to-wafer hybrid bonding, wafer-to-wafer bonding en geavanceerde substraten.

Versnelde hybrid bonding van matrijs tot wafer

Die-to-wafer hybrid bonding gebruikt directe koper-naar-koper interconnecties om de I/O-dichtheid te verhogen en de bedradingslengte tussen chiplets te verkorten om de algemene prestaties, het vermogen en de kosten te verbeteren. Om de ontwikkeling van deze technologie te versnellen, voegt Applied geavanceerde software modellering en simulatie toe aan zijn Advanced Packaging Development Center. Met deze mogelijkheden kunnen verschillende parameters, zoals materiaalkeuze en verpakkingsarchitectuur, worden geëvalueerd en geoptimaliseerd voordat de hardware wordt ontwikkeld, zodat de leercycli aanzienlijk worden versneld en klanten sneller een product op de markt kunnen brengen. Dit bouwt voort op de gezamenlijke ontwikkelingsovereenkomst die in oktober 2020 werd aangekondigd tussen Applied en BE Semiconductor Industries N.V. (Besi) om de eerste complete en bewezen apparatuur-oplossing in de industrie te ontwikkelen voor die-based hybrid bonding.

“Ons gezamenlijk ontwikkelingsprogramma met Applied Materials heeft ons gezamenlijk inzicht in de geoptimaliseerde apparatuur-oplossingen die nodig zijn voor klanten om complexe hybride bondingprocessen te gebruiken in productieomgevingen op waferniveau, sterk verbeterd”, aldus Ruurd Boomsma, Chief Technology Officer van Besi. “In zeer korte tijd hebben de teams van Besi en Applied uitstekende vooruitgang geboekt door samen te werken in het Hybrid Bonding Center of Excellence in Singapore om materialen van klanten te verwerken en de ontwikkeling van geavanceerde heterogene integratietechnologieën te versnellen.”

Ontwikkeling van geoptimaliseerde oplossingen voor wafer-naar-wafer hybrid bonding

Wafer-to-wafer bonding stelt chipmakers in staat om bepaalde chipstructuren op één wafer te bouwen en andere op een tweede wafer, en vervolgens de wafers te lijmen om complete apparaten te maken. Om hoge prestaties en rendement te bereiken, is de kwaliteit van de front-end processtappen van cruciaal belang, net als de precieze uniformiteit en uitlijning van de wafers terwijl ze worden gelijmd. Applied kondigde vandaag een gezamenlijke ontwikkelingsovereenkomst aan met EV Group (EVG) om geoptimaliseerde oplossingen te ontwikkelen voor wafer-to-wafer bonding. De samenwerking brengt de expertise van Applied in halfgeleiderprocessen op het vlak van depositie, planarisatie, implantatie, metrologie en inspectie samen met EVG’s leiderschap in wafer bonding, wafer voorbehandeling en activering, alsook uitlijning en bond overlay metrologie.

Lees Link magazine digitaal of vraag een exemplaar op: mireille.vanginkel@linkmagazine.nl’

“Halfgeleiderinnovatie wordt steeds meer gevoed door 3D-integratie en speciale materialen, waardoor de vraag naar wafer-to-wafer hybride verlijming toeneemt. Het optimaliseren van dit kritische proces voor nieuwe toepassingen vereist een diepgaand begrip van integratieproblemen zowel boven als onder in de procesketen,” zegt Dr. Thomas Uhrmann, Business Development Director bij EVG. “Industriële samenwerkingen zoals die met Applied Materials stellen ons in staat om gegevens te delen en te leren van verschillende sterke punten van procesapparatuurbedrijven, waardoor we onze oplossingen kunnen co-optimaliseren en de opkomende en kritieke productie-uitdagingen van onze klanten beter kunnen oplossen.”

Applied wil meer samenwerking

“Door samen te werken met industriële partners zoals Besi en EVG, biedt Applied Materials onze klanten de mogelijkheden en expertise die ze nodig hebben om de ontwikkeling en adoptie van hybride bonding technologieën te versnellen, zowel die-to-wafer als wafer-to-wafer,” zegt Vincent DiCaprio, Managing Director of Business Development for Advanced Packaging bij Applied Materials. “Applied kijkt ernaar uit om verdere verbintenissen in het ecosysteem aan te gaan, aangezien chipmakers steeds vaker heterogene ontwerptechnieken gebruiken om hun PPACt-roadmaps te sturen.”