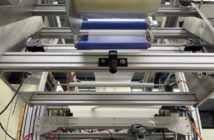

Tijdens de Symposia on VLSI Technology and Circuits van 2018, demonstreert imec, ’s werelds toonaangevende onderzoeks- en innovatiehub in nano-elektronica en digitale technologie, het ultramoderne spin-orbit koppel MRAM (SOT -MRAM) apparaten op 300 mm-wafels met behulp van CMOS-compatibele processen. Met een onbeperkt uithoudingsvermogen (> 5×1010), een hoge schakelsnelheid (210ps) en een energieverbruik tot slechts 300pJ behalen de SOT-MRAM-apparaten vervaardigd in een 300mm-lijn dezelfde of betere prestaties als labapparaten. Deze MRAM-technologie van de volgende generatie is bedoeld om L1 / L2 SRAM-cachegeheugens te vervangen in krachtige computertoepassingen.

SOT-MRAM is onlangs ontstaan als een niet-vluchtige geheugentechnologie die een hoge uithoudingsvermogen en een laag stroomverbruik, sub-ns schakelsnelheid belooft. Met deze eigenschappen kan het de beperkingen van het spinoverdrachtskoppel MRAM (STT-MRAM) voor L1 / L2 SRAM-cachegeheugenvervanging overwinnen. SOT-MRAM-apparaatmodules op 300 mm-wafels met behulp van CMOS-compatibele processen.

De kern van het SOT-MRAM-apparaat is een magnetische tunnelovergang die is ingeklemd tussen een magnetische vaste laag en een magnetische vrije laag. Vergelijkbaar met STT-MRAM operatie, door middel van het schakelen van de magnetisatie van deze vrije magnetische laag, door middel van een stroom. In STT-MRAM wordt dit huidige magnetische veld verwisseld met de magnetische tunnelovergang en hetzelfde pad wordt herhaald. In een SOT-MRAM-inrichting daarentegen wordt het schakelen van de vrije magnetische laag uitgevoerd door een in-vlak stroom in een aangrenzende SOT-laag te injecteren – typisch gemaakt van een zwaar metaal. Vanwege de huidige injectiegeometrie zijn het lees- en schrijfpad ontkoppeld, waardoor het uithoudingsvermogen en de leesstabiliteit van het apparaat aanzienlijk worden verbeterd.

Gouri Sankar Kar, Program Director Imec

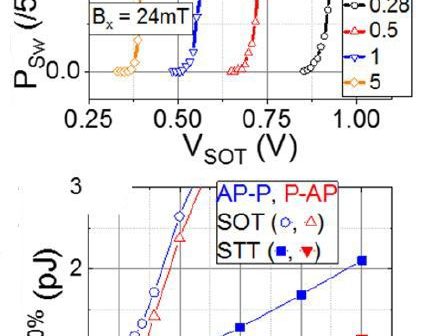

Imec heeft het SOT- en STT-schakelgedrag vergeleken met één en hetzelfde apparaat, gefabriceerd op 300 mm wafers. Hoewel de schakelsnelheid tijdens de STT-MRAM-bewerking beperkt was tot 5ns, werd tijdens de werking van SOT-MRAM betrouwbaar overschakelen naar 210 pingen gedemonstreerd. De SOT-MRAM-apparaten hebben een onbeperkt uithoudingsvermogen (> 5×1010) en een werkingsvermogen van slechts 300 pJ. Loodrecht gemagnetiseerde stapel met beta-fase wolfraam (W) voor de SOT-laag.

“STT-MRAM-technologie heeft een groot potentieel voor het vervangen van L3-cachegeheugen in krachtige computertoepassingen”, aldus Gouri Sankar Kar, Distinguished Member of Technical Staff bij imec. Vanwege de toenemende betrouwbaarheid en toegenomen nergie bij sub-ns-schakelsnelheden zijn ze echter niet geschikt om de snellere L1 / L2 SRAM-cachegeheugens te vervangen. SOT-MRAM-technologie wil ons helpen de MRAM-bewerking uit te breiden naar het SRAM-toepassingsdomein. Door deze MRAM-technologie van de volgende generatie in het laboratorium is bewezen, hebben we nu de volwassenheid van de technologie aangetoond. “

Deze resultaten zullen worden gepresenteerd op het VLSI Circuits Symposium op 20 juni in de sessie C8 Emerging Memory. Imec’s onderzoek in geavanceerd geheugen wordt uitgevoerd in samenwerking met de belangrijkste partners van imec in haar kern CMOS-programma’s, waaronder GlobalFoundries, Huawei, Micron, Qualcomm, Sony Semiconductor Solutions, TSMC en Western Digital.