MoS2 is een 2D materiaal, wat betekent dat het in stabiele vorm kan worden gekweekt met bijna atomaire dikte en atomaire precisie. Imec synthetiseerde het materiaal tot op één laag (0,6nm dikte) en vervaardigde apparaten met geschaald contact en kanaallengte, zo klein als respectievelijk 13nm en 30nm. Deze zeer geschaalde afmetingen, gecombineerd met de geschaalde dikte van het gate oxide en de high K dielectric, hebben de demonstratie van enkele van de beste apparaatprestaties tot nu toe mogelijk gemaakt. Het belangrijkste is dat deze transistors een uitgebreide studie van de fundamentele eigenschappen van het apparaat en de kalibratie van TCAD-modellen mogelijk maken. Het gekalibreerde TCAD-model wordt gebruikt om een realistisch pad voor prestatieverbetering voor te stellen. De hier gepresenteerde resultaten bevestigen het potentieel van 2D-materialen voor extreme transistorschaalvergroting – wat zowel de hoogwaardige logische als geheugentoepassingen ten goede komt.

We dragen dit inzicht over naar ons 300mm-wafer-platform voor transistors met 2D-materialen, dat vorig jaar op het IEDM werd aangekondigd.”. Beeld Imec

Theoretische studies bevelen 2D materialen aan als het perfecte channel material voor extreme transistorschaalvergroting, aangezien er slechts weinig korte kanaaleffecten worden verwacht in vergelijking met de huidige op Si gebaseerde apparaten. Tips van dit potentieel zijn al gepubliceerd met one-of-a-kind transistors gebouwd op natuurlijke vlokken van 2D materialen.

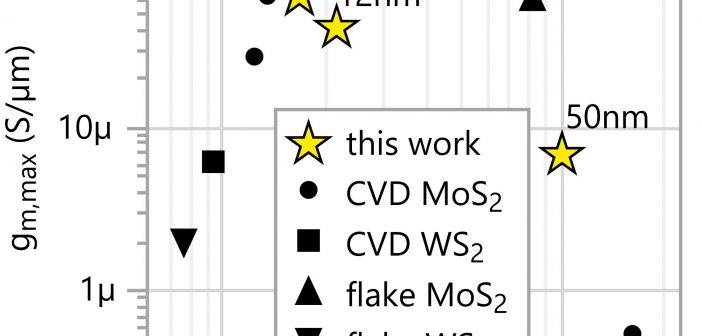

Voor het eerst heeft imec deze theoretische bevindingen getest door middel van een uitgebreide set van 2D-materiaal-gebaseerde transistorgegevens. De apparaten met de kleinste footprint hebben een kanaallengte van 30nm en <50nm contact pitch. Op stroom tot 250µA/µm is gedemonstreerd met 50nm SiO2 gate diëlektricum. Op een stroom van ~ 100 µA/µm en een uitstekende SSmin van 80mV/dec (voor VD = 50mV) zijn aangetoond met 4nm HfO2 in een achtergrondconfiguratie. De prestaties van het apparaat worden niet beïnvloed door de schaling van de contactlengte, wat bevestigt dat de dragers vanaf de rand van het contactmetaal rechtstreeks in het kanaal worden geïnjecteerd, in lijn met TCAD-simulaties. Het werk bevestigt dat TCAD-modellen grote delen van de apparaatfysica vastleggen en experimentele validatie en het in kaart brengen van de toepassingsruimte begeleiden. Een deel van het papier dat wordt gepresenteerd op het IEDM, is gewijd aan het instellen van de weg voor apparaatoptimalisatie voor het bereiken van Si-like prestatiedoelen.

“Hoewel we nog steeds een orde van grootte verwijderd zijn van de Si transistors, hebben we onze MOSFET-apparaten in een wereld gebracht waar ze veelbelovende prestaties laten zien voor toekomstige logic en geheugentoepassingen”, zegt Iuliana Radu, directeur van Exploratory and Quantum Computing imec. “Om deze orde van grootte te overbruggen, hebben we een pad van systematische verbeteringen geïdentificeerd, zoals een verdere vermindering van de dikte van het poortoxide, de implementatie van een dubbel gesloten architectuur en een verdere vermindering van kanaal- en interfacedefecten. We dragen dit inzicht over naar ons 300mm-wafer-platform voor transistors met 2D-materialen, dat vorig jaar op het IEDM werd aangekondigd.”.

Luc Van den Hove, CEO van imec Foto Imec

“Als wereldleider op het gebied van onderzoek en innovatie is het de rol van imec om de schaalvergroting van apparaten tot het uiterste te beperken. We gaan deze uitdaging aan door verschillende schaalmogelijkheden te onderzoeken, optimale projecties te leveren en de industrie te begeleiden bij de toepassing van de voorgestelde oplossingen, aldus Luc Van den Hove, CEO van imec. “Onze partners verwachten dat wij het voortouw nemen en hen ondersteunen bij het realiseren van hun roadmaps door het potentieel van innovatieve concepten en nieuwe materialen te demonstreren. Daarom ben ik zo blij dat we uitstekende prestaties hebben laten zien in ultraschaalapparatuur met 2D-materialen en een geloofwaardige weg naar verdere verbeteringen gericht op massaproductie in industriële 300mm-fabrieken”.