Stephen Renwick, Director of Imaging Physics at Nikon Research Corporation of America,

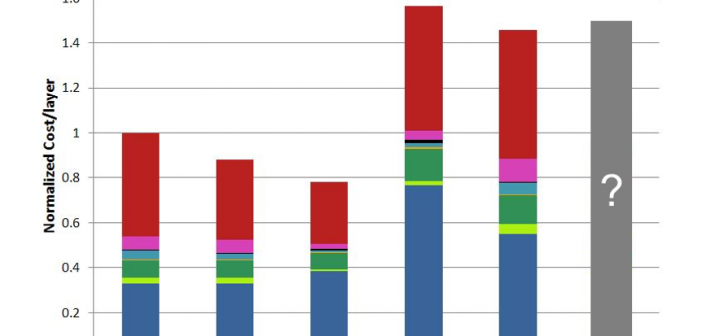

Stephen Renwick, Director of Imaging Physics at Nikon Research Corporation of America, zegt dat 7 nanometer-node logic-chiptechnologie naar verwachting voornamelijk zal worden gerealiseerd met 193i-lithografie. ‘EUV zal moeite hebben om klaar te zijn voor 5 nanometer, beperkt door opbrengstproblemen veroorzaakt door stochastische effecten in de resist’, aldus Renwick. ‘Klaar of niet, het zal wel worden gebruikt.’ Renwick suggereert dat de invoering van multiple-patterning met EUV wellicht nodig is, maar de kosten zou verhogen. ‘193i-lithografie zal nog steeds worden gebruikt met viervoudige patronen en in combinatie met andere technieken – er is niet één oplossing.’ Bij de keuze tussen immersielithografie en EUV voor verschillende klantensegmenten op 5 nanometer, merkt Renwick op dat de kosten afhankelijk zijn van de laag. ‘Enige tijd geleden hebben we berekend dat de kosten van ofwel 193i triple-patterning ofwel 193i SADP met twee cuts ongeveer gelijk waren aan single-patterning met EUV’, legt Renwick uit. ‘Dat stemde overeen met de openbare schattingen van chipmakers en betekende dat de keuze voor de lithografiemethode meer afhankelijk was van de precieze toepassing.’

Andere uitdagingen die Renwick aan de horizon voor EUVL op 5 nanometer ziet, zijn stochastische effecten in EUV-resists. ‘Het is onwaarschijnlijk dat deze effecten verdwijnen zonder de lithodosis te verhogen, wat de doorvoersnelheid verder zal aantasten.’ Aldus Renwick tegenover Deb Vogler van Solid State Technology.

Renwick doet zijn verhaal tijdens de Advanced Lithography TechXPOT van dit jaar op SEMICON West op 12 juli. Daar is het thema de voortgang van extreme ultraviolette lithografie (EUVL) en zijn economische levensvatbaarheid voor high-volume manufacturing (HVM), evenals andere lithografieoplossingen mogelijk geschikt voor 5 nanometer-lithografie. Ook Michael Lercel, Director of Strategic Marketing van ASML, is er een van key note speakers.