Vandaag demonstreert onderzoekscentrum imec op de toonaangevende wetenschappelijke conferentie VLSI Technology and Circuits de eerste volledig functionele en geïntegreerde forksheet-transistor. Onderzoekers van imec slaagden erin om met een soort vorkstructuur de afstand tussen transistoren, de bouwstenen van een chip, aanzienlijk te verkleinen, wat chipproducenten toelaat om onder de technologienode van 2 nanometer te duiken en dus krachtigere chips te ontwikkelen.

Chips worden ieder jaar krachtiger. De voorbije jaren maakte die technologische vooruitgang vooral onze computers of smartphones sneller en energiezuiniger, maar de komende jaren zullen chips in zowat ieder toestel geïntegreerd worden. Zo zullen slimme gezondheidssensoren via lab-op-chiptechnologie sneller ziektes kunnen opsporen of zullen zelfrijdende wagens geavanceerde chips nodig hebben om snel te kunnen reageren op een voorbijlopende voetganger. Samen met de razendsnelle ontwikkelingen in artificiële intelligentie, het toenemende dataverkeer en de introductie van 5G-en 6G-netwerken, zal de vraag naar meer geavanceerde chips gigantisch toenemen

Het aantal transistoren op een chip verdubbelt zowat om de twee jaar, waardoor er steeds meer rekenkracht op een kleinere oppervlakte beschikbaar wordt. Op een bepaald punt botsen we echter op fysieke limieten en wordt het een technologisch huzarenstukje om nog nieuwe transistorarchitecturen te ontwikkelen die deze schaalverkleining kunnen voortzetten

Als toonaangevend onderzoekscentrum voor nano-elektronica is het imecs rol om tien jaar vooruit te denken en om voortdurend nieuwe technologische routes te verkennen. Dankzij de unieke apparatuur die aanwezig is de 300mm cleanroom in Leuven, kan imec deze nieuwe ideeën uittesten en ontwikkelen. Partners van imec (zoals TSMC, Samsung of Intel) kunnen er vervolgens voor kiezen om deze innovaties te integreren in hun volgende generatie chips. In de nanometerwedloop die vandaag gaande is, plannen de producenten van geavanceerde chips enorme investeringen om de komende jaren de stap te zetten van de 5 nanometer-technologienode naar 3 nanometer en vervolgens naar 2 nanometer en kleiner. De nieuwe forksheet-technologie, die imec nu demonstreert, kan hen helpen in het nemen van die laatste horde

Van een ‘vin’ naar een ‘vork’

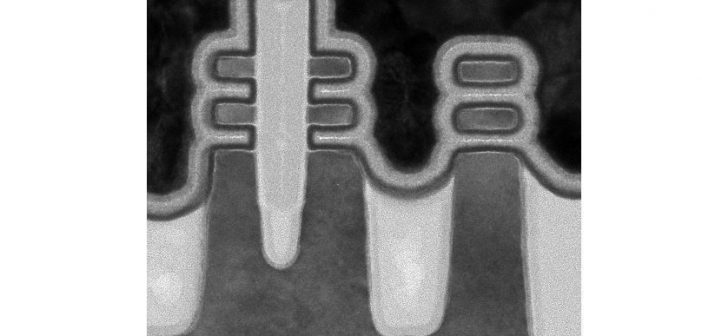

Vandaag vinden we in de meest geavanceerde chips voor reken- en geheugentoepassingen (de technologienodes van 5 en 7 nanometer) de FinFET terug. De FinFET dankt zijn naam aan een geleidingkanaal dat de vorm van een ‘vin’ heeft. Deze transistor werd een twintigtal jaar geleden uitgevonden en ontstond uit de MOSFET – de transistor die de schaalverkleining en massaproductie van computerchips heeft mogelijk gemaakt. Terwijl bij de planaire MOSFET de poort die de stroomstootjes regelt alleen controle voert langs de bovenkant, omgeeft de poort bij de FinFET het geleidingskanaal langs drie kanten, met minder lekstromen (stroomverlies) tot gevolg. Vanaf volgend jaar zal de FinFET geleidelijk aan plaatsmaken voor de zogenaamde gate-all-around nanosheet-transistor, waarbij de poort het kanaal aan álle kanten zal omgeven. Voor al deze transistor-types heeft imec cruciaal R&D-werk verricht, steeds in samenwerking met zijn partners

Ook de nanosheet-transistor zal echter ooit op zijn limieten botsen waardoor de transistoren niet dichter bij elkaar kunnen worden gebracht. De forksheet, een concept dat enkele jaren geleden door imec werd uitgevonden, biedt hiervoor een oplossing. De forksheet ontleent zijn naam aan zijn vorkstructuur, die een veel nauwere afstand tussen de transistoren mogelijk maakt in vergelijking met FinFET of met nanosheets. Imec toonde eerder al via simulaties aan dat de forksheet de nanosheet overtreft op gebied van schaalverkleining en performantie

Nu is imec er voor het eerst in geslaagd om goed werkende forksheets te maken die compatibel zijn met standaard chipproductieprocessen op 300mm wafers (siliciumschijven). Op de wetenschappelijke conferentie VLSI Technology and Circuits demonstreren onderzoekers van imec de eerste volledig functionele elektrische karakterisatie ervan. Om benchmarking mogelijk te maken zijn de forksheet-transistoren en nanosheet-transistoren samen geïntegreerd op een wafer. Ze vertonen gelijkaardige performantie, maar de transistoren kunnen in deze nieuwe architectuur veel dichter bij elkaar geplaatst worden: 35 procent dichter dan wat vandaag met de huidige FinFET-technologie mogelijk is.